Inovasense Blog

Odborné perpektívy na hardvérové inžinierstvo, IoT inovácie a technologickú suverenitu EÚ.

EN 18031: Čo samohodnotenie skutočne vyžaduje

Čo EN 18031 samohodnotenie (Modul A) skutočne vyžaduje — a kde sa najčastejšie vyskytujú zdokumentované medzery vo vývoji pripojeného hardvéru.

ESP32 vs STM32: Ktorý MCU pre váš ďalší produkt?

ESP32 alebo STM32? Porovnanie architektúry, konektivity, spotreby, ceny a ekosystému. Rozhodovací rámec pre IoT, priemyselné a spotrebné produkty.

Legislatíva EÚ pre Hardvér 2026: Kompletný Sprievodca

Šesť nariadení EÚ zmení výrobu hardvéru v 2026 — od CRA hlásení zraniteľností po Digitálny Pas Produktu. Časový plán pre výrobcov.

FPGA vs ASIC 2026: Rozhodovací Rámec

FPGA alebo ASIC? Porovnanie nákladov, výkonu, spotreby, času uvedenia na trh a flexibility. Kalkulačka NRE a rozhodovací rámec pre inžinierov.

Kontrola Vývozu Dual-Use v EÚ 2026

Delegované nariadenie EÚ 2025/2003 rozšírilo kontroly dvojakého použitia na FPGA, kvantové komponenty a pokročilé polovodiče. Sprievodca súladom.

EÚ CRA: Checklist Súladu pre Hardvér

Zákon o kybernetickej odolnosti nariaďuje bezpečné bootovanie, správu zraniteľností a SBOM pre všetky pripojené produkty v EÚ. Kompletný checklist.

Čo je Edge Computing? Kompletný Sprievodca

Architektúra edge computingu pre hardvérových inžinierov. Spracovateľský hardvér (FPGA, GPU, NPU), úrovne latencie, priemyselné use cases a EÚ zhoda.

Čo je FPGA? Kompletný Sprievodca (2026)

Čo je FPGA, ako funguje a prečo je dôležité. Architektúra, programovanie, reálne aplikácie, náklady a porovnanie FPGA s CPU, GPU a ASIC.

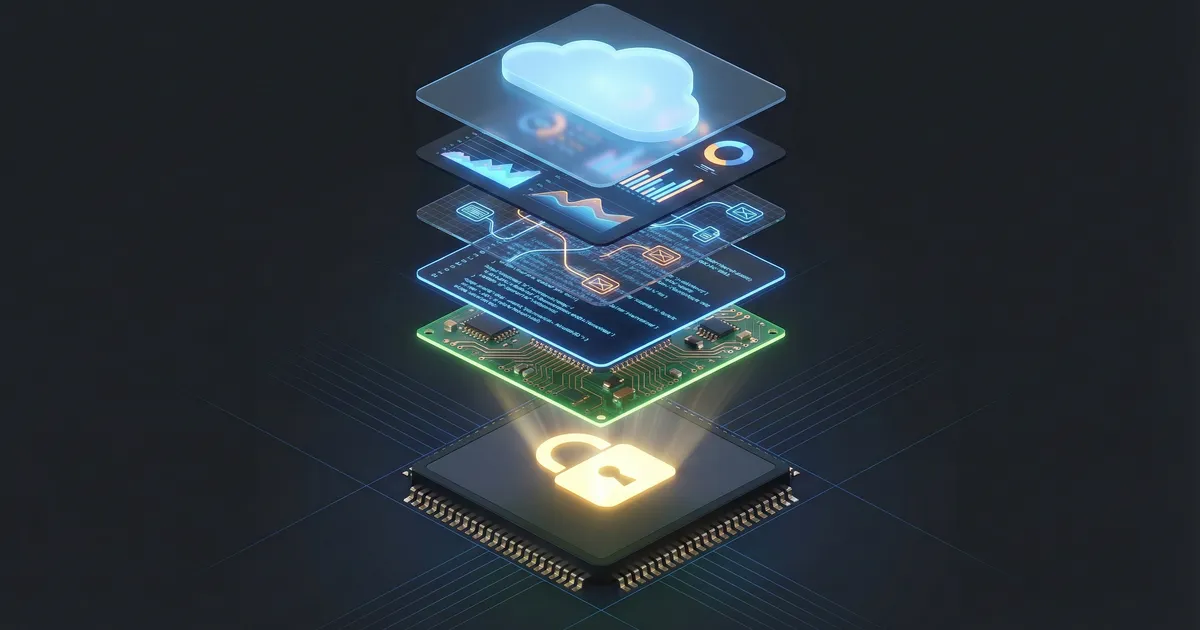

IoT Bezpečnosť: Sprievodca pre HW Inžinierov

Prekročte softvérové firewally. Hardvérová IoT bezpečnosť: secure boot reťazce, TPM vs secure element a FPGA bitstream ochrana v praxi.

EÚ Compliance: CE, CRA a RED Sprievodca

EÚ compliance pre elektroniku vyžaduje CE značenie, Zákon o kybernetickej odolnosti, delegované akty RED a súlad s AI Act. Kompletný sprievodca.

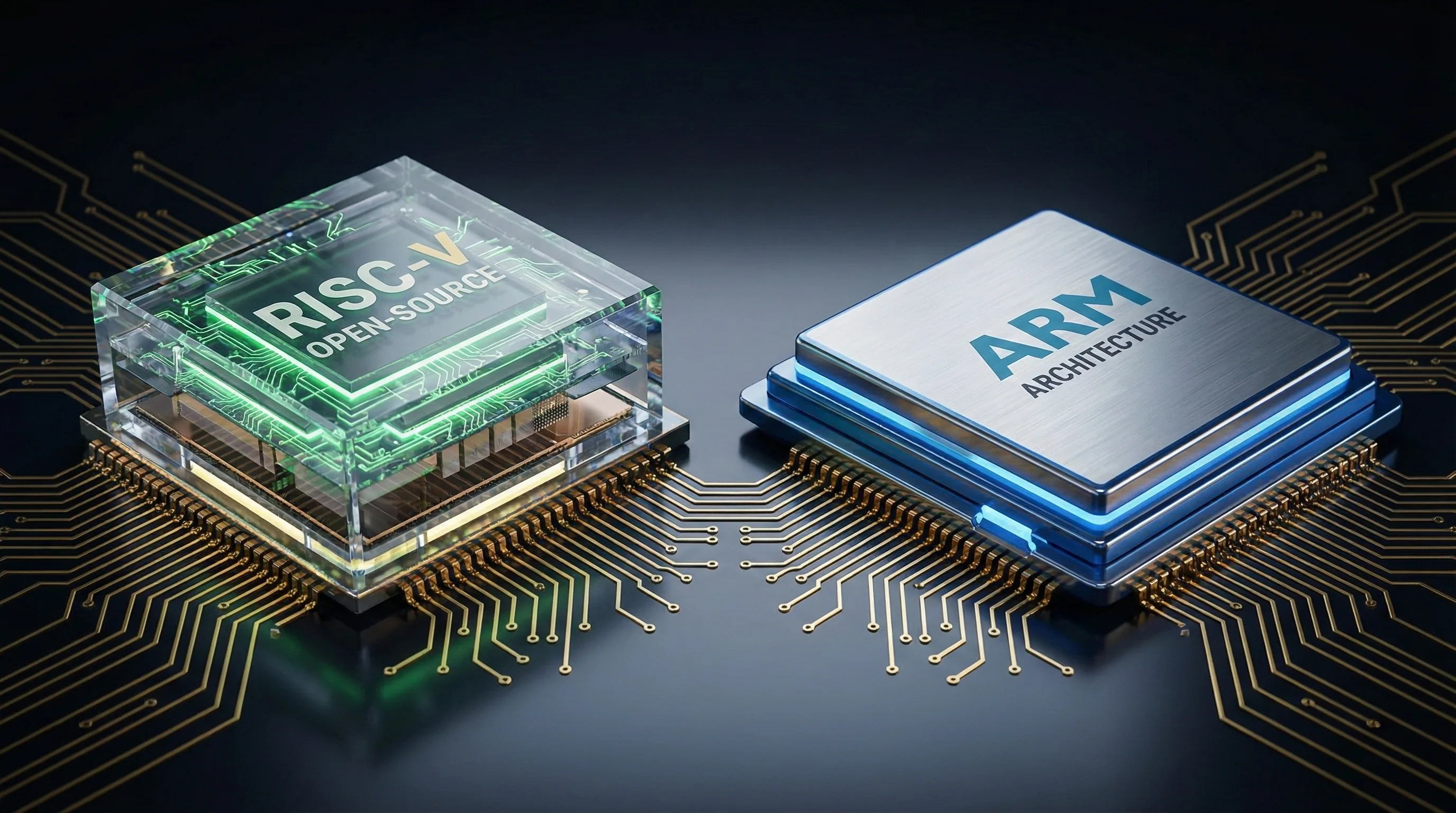

RISC-V vs ARM: Architektúra pre Embedded

Porovnanie RISC-V vs ARM pre embedded inžinierov. Rozdiely ISA, reálne benchmarky, zrelosť ekosystému, náklady a dôsledky pre EÚ suverenitu.

Bezpečnosť Hardvéru: Kompletný Sprievodca

Hardvérová bezpečnosť znamená dôveru v kremíku — Secure Elements, TPM, PSA Certified MCU a bezpečný boot. Kompletný sprievodca.

Edge AI v Priemyselných Aplikáciách

Edge AI umožňuje inferenciu pod 10 ms na mikrokontroléroch a FPGA. Ako on-device ML mení zdravotníctvo, výrobu a autonómne systémy.

Made in EU: Výhoda HW Vývoja v Európe

Vývoj hardvéru v EÚ ponúka regulačný súlad, ochranu IP, odolnosť dodávateľského reťazca a stimuly Chips Act. Kompletný strategický prehľad.

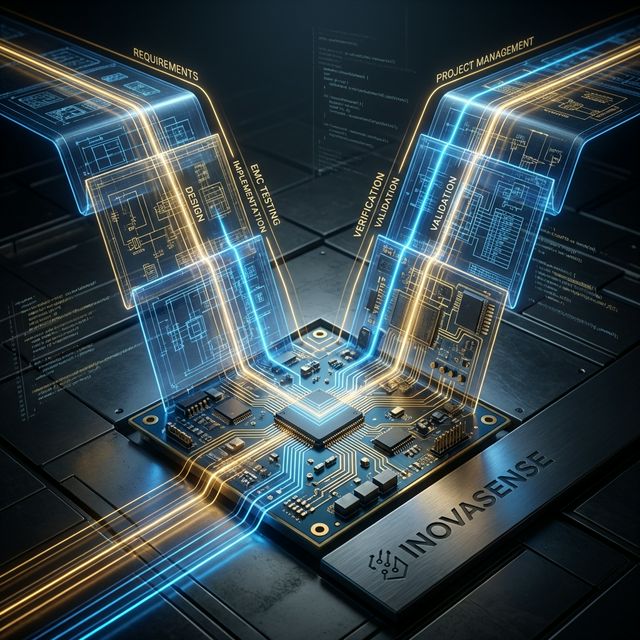

V-Model: Metodológia pre Elektroniku

Štruktúrovaný V-model vo vývoji elektroniky predchádza nákladným prepracovaniam PCB, zlyhaniam EMC a oneskoreniam certifikácie. Kompletná metodika.

Outsourcing HW Vývoja: Sprievodca

Outsourcovaný vývoj hardvéru skracuje čas uvedenia na trh o 30–50 %. Kritériá hodnotenia partnerov, modely spolupráce a ochrana IP.

Outsourcing HW: Maximalizácia ROI

Outsourcing vývoja hardvéru skracuje čas uvedenia na trh o 30–50 % a ušetrí 500 tis. – 2 mil. € CapEx. Kedy a ako outsourcovať.

IoT Vysvetlené: Technický Sprievodca

IoT prepája zariadenia cez senzory, MCU a bezdrôtové protokoly na zber dát v reálnom čase. Od kremíku po cloud v roku 2026.

Vstavané Programovanie: RTOS a HW

Vstavaný programovanie je tvorba softvéru pre mikrokontroléry a dedikovaný hardvér. C/C++, RTOS, ladenie cez JTAG/SWD a trendy v roku 2026.